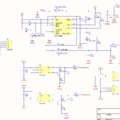

Kis heads-up: megterveztem a DDS Jelgenerátorom, és meg is építettem, rettenetes anyázások közepette, kb. 1 hónap alatt. Mikkel szerencsétlenkedtem?

- A NYÁK nagyon szép lett, teljesen új koncepcióval dolgoztam, épp csak 120 via lett rajta. Na ezeket mire mind beforrasztottam, azt hittem megőszülök. Ha megengedhetném magamnak, vagy gyártatnám a paneljaimat, vagy valami rendes furatfémezési módszer után néznék...

- Amivel nem volt baj, az a 0.2 vezető - 0.2 szigetelő szélesség, 2 oldalon. a két oldal között kb 0.2mm elcsúszást sikerült összehoznom, kicsit vigyázni kellett a fúróval. Ja, a nagy vigyázás közben el is törtem egy fúróhegyet...

- Az üres részeket kitöltöttem telefölddel, ez bekúszott az SMD cuccok lába közé, és marha könnyen rövidre záródott forrasztás közben - na ezt a hibát nem követem el újra.

- Az FPGA kapott maga alá egy föld plane-t, amit olyan ügyesen körbevettem a tápvonalakkal, hogy teljesen elvágódott a rendes földemtől. A nyáktervező progim persze nem szólt, biztos volt még szerinte olyan 0.1mm valahol, ami nekem lemaródott. Hejj de fogtam a fejem amikor ezt észrevettem...

- A tápok szépen feléledtek (lassan már dc-dc konverterekkel álmodok), beraktam a PIC-et, bekapcsolom, semmi. Rengeteget gondolkoztam miért nem működik, aztán kiderült hogy a ledeket más lábra tettem, így jóhogy nem világítottak, az USB-n meg volt egy sense, amit nem kötöttem be (USB-ről kapja a tápot, nyilván van USB mire feltápászkodik), de a programból nem vettem ki, persze hogy nem indult. Szoftveres reszelgetés után már gyönyörű.

- Deviszont a PIC-en felcseréltem az I2C-hez az SCL és az SDA lábakat, szörnyen szidtam magam miatta, átmadzagoltam.

- Az FPGA ezek után már viszonylag fájdalommentesen bekerült, és szépen működött is. Forrasztás közben vagy összesen 20 lábát zártam össze, jó móka volt utána takarítani.

- Ekkor vettem észre, hogy olyan tokozású DAC-ot terveztem bele, ami nem volt itthon, úgyhogy rendelhettem a farnelltől (másnapra itt volt :D )

- Viszont egyszer már elbaltáztam az AD8000-es opamp lábkiosztását, és persze a rossz rajzról hoztam át a véglegesre, úgyhogy ezzel rengeteget szívtam mire bedrótoztam a helyére a kis lábnélküli smd szart.

- Egyébként kb a felénél vettem észre, hogy az egész elvi hibás, ha az FPGA-t a PIC mellé rakom és nem alá, minimálisan nagyobb panelon sokkal rövidebb tápokkal-földekkel megúsztam volna.

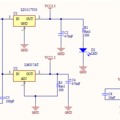

- Ettől teljesen függetlenül a DC-DC konverterek úgy zajonganak mint egy állat. A kimenő jelen olyan gyönyörű 50mVpp 1MHz zaj figyel hogy öröm nézni. Nagyon bíztam benne, hogy most így az előzőekből okulva, rendes NYÁKtervvel, szép széles teliföldekkel csökkenthető a zaj, de úgy tűnik nem. Ez kb azt is jelenti, hogy vissza a tervezőasztalhoz, vissza az analóg, melegedő, de legalább csendes tápokhoz, és replay!

Hát ezzel megint elleszek egy hónapig nagyjából, ha két rétegen megvan a cucc, megtervezem négyrétegűre, és gyártatok belőle párat. Ez már nagyjából az első release verzió lesz, az alpha és a két béta után...

Közben megrendeltem pár alkatrészt a DSO-mhoz is, aminek ugye a PIC és az FPGA része ugyanez lesz, csak az analóg bemenettől az ADC-ig kell megrajzolnom, kikísérletezni, mennyire használhatóak a relék, meg mindenféle elvetemült fícsörön gondolkozni mint pl. mintavételi sebesség duplázás két ADC-vel, meg analóg trigger, meg ETS, de ez már a jövő zenéje.

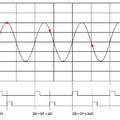

Szerk.: A lényeget nem is mondtam, megvan a 200 MSPS, vagyis 50MHz szinusz. Az FPGA, a DAC és az erősítők is nagyon jól viselik (csak a szkópommal nem tudom rendesen megmérni :) úgyhogy új táp kell csak és kész. Találtam egy ígéretes táp kapcsolást, talán még olyan vészesen meleg se lesz...